为什么存储器接口对传递过来的地址,是有要求的?譬如64位存储器,要求地址是8的倍数?

0

文章中看到DDR3 这个64位的存储器接口规定传递过来的地址是8的倍数,针对这个问题,有人说因为一次数据传输是64位啊,所以接口这样规定,但是这样的回答貌似太没有说服力了,有谁能从原理上解析下原因呢?

我们知道64位存储器数据传输一次8个字节,内存是按字节编址,假如我们访问0001这个编号的内存地址上的一个字节数据,实际返回的是0000-0007地址区间内的数据,然后CPU再拆解获得正确数据,假如我们刚好将一个32位的int数据 存放在0006地址开始的内存,那就会占据了0006-0009地址空间,而CPU取数据就要分2次了去取,一次0000-0007,第二次0008-0015,两次的数据拆分组合后获取正确数据。所以很多在存放数据的时候按照内存对齐,减少取数次数。不过即使这样的话,跟规定传递过来的地址必须是8的倍数又有什么关联呢,最好从硬件电路实现原理的角度解释一下这个

所有回答(3)

0

个人认为是因为存储的最小单位是字节,读写都是以字节为单位。至于为什么设计成一个字节为8bit,我也不太清楚,可能刚开始就是这样设计的,慢慢成了标准吧。

这是我刚搜索到的:

0

串行并行计算机无处不在。

你可以了解移位寄存器、2位、4位等单片机。

规定4个bit都是可以的,只需要等待本身的64/4个周期就行了。

说到这里,你应该想明白为什么规定特定频率,还有什么叫倍频。

0

这位同学这么好学,来来来,

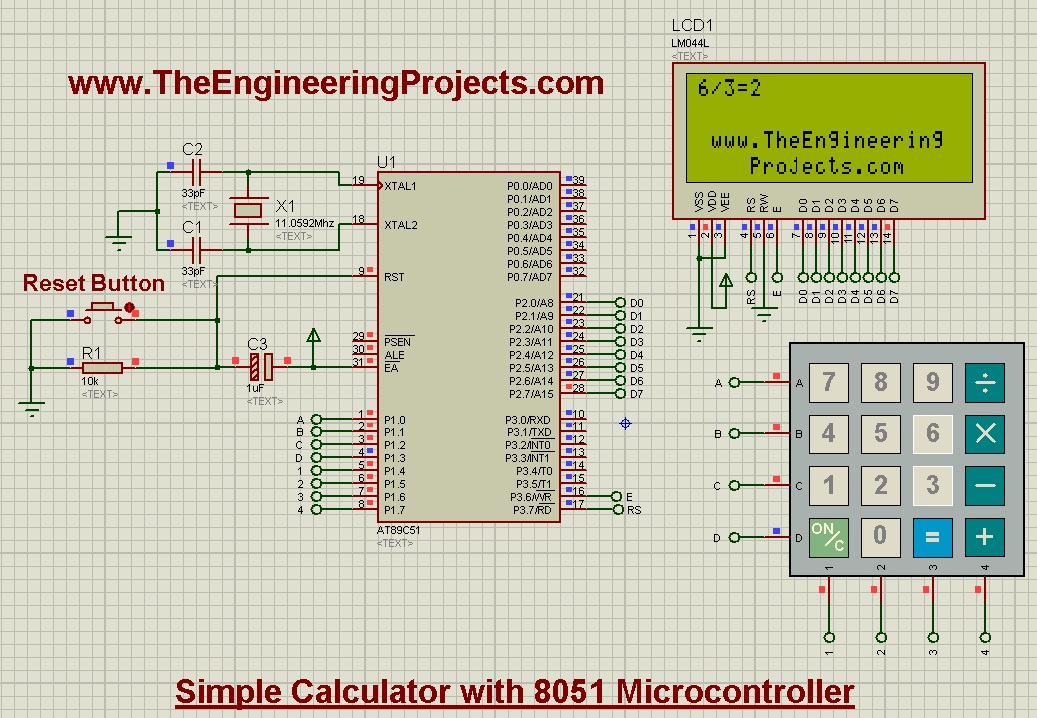

先上个图

然后建议你找一本大学的《数字电路和模拟电路》,那上面有。